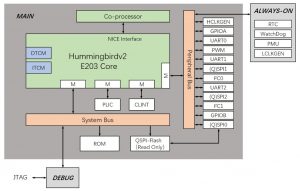

首先看下芯片的架构如下图:

上图取用官方git,其参考文档里也有展示。

麻雀虽小五脏俱全,一颗芯片该有的都有了。有个快速参考的文档页面:

https://doc.nucleisys.com/hbirdv2/

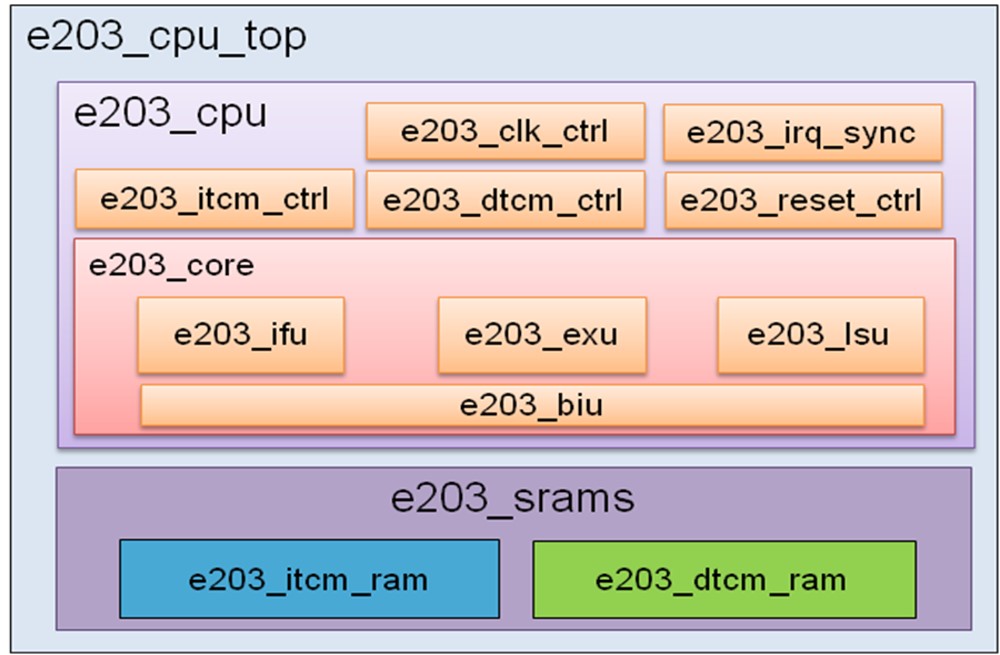

蜂鸟Hummingbirdv2 E203 Core的结构如下图:

他有如下特性:

- RISC-V RV32IMAC or RV32EMAC ISA supported

- 2-Stage Pipeline

- Machine Mode only

- Configurable

- “RISC-V External Debug Support Version 0.11nov12” supported

- NICE(Nuclei Instruction Co-unit Extension) supported

用户通过配置config.v file (in e203_hbirdv2/rtl/e203/core目录里)实现不同功能 ,

比如定义是否有ITCM,以及其大小。是否有DTCM和其base address.

蜂鸟E203处理器核模块架构:

1. 顶层模块结构

e203_cpu_top作为最顶层模块,仅包含e203_cpu(逻辑部分)和e203_srams(SRAM部分)两个子模块,这种划分便于ASIC实现

采用层次化设计,将存储单元与逻辑单元分离,符合低功耗处理器设计理念

2. 核心控制模块

e203_clk_ctrl:实现处理器各组件自动时钟门控,是低功耗设计的关键模块

e203_reset_ctrl:将外部异步复位信号转换为”异步置位同步释放”的复位信号

e203_irq_sync:对外部异步中断信号进行同步处理

3. 存储子系统

e203_itcm_ctrl/e203_dtcm_ctrl:分别控制指令紧耦合存储器(ITCM)和数据紧耦合存储器(DTCM)的访问

e203_itcm_ram/e203_dtcm_ram:实现物理存储单元,采用SRAM结构

4. 处理器核心流水线

e203_core作为主逻辑模块包含:

- e203_ifu:取指单元,负责指令预取

- e203_exu:执行单元,完成算术逻辑运算

- e203_lsu:访存单元,处理加载/存储操作

- e203_biu:总线接口单元,连接外部总线

采用2级流水线结构,支持RISC-V RV32IMAC/RV32EMAC指令集

5. 时钟设计特点

需要16MHz主时钟和32.768KHz低频时钟双时钟域

FPGA移植时通常通过MMCM/PLL生成16MHz时钟,再分频得到32.768KHz

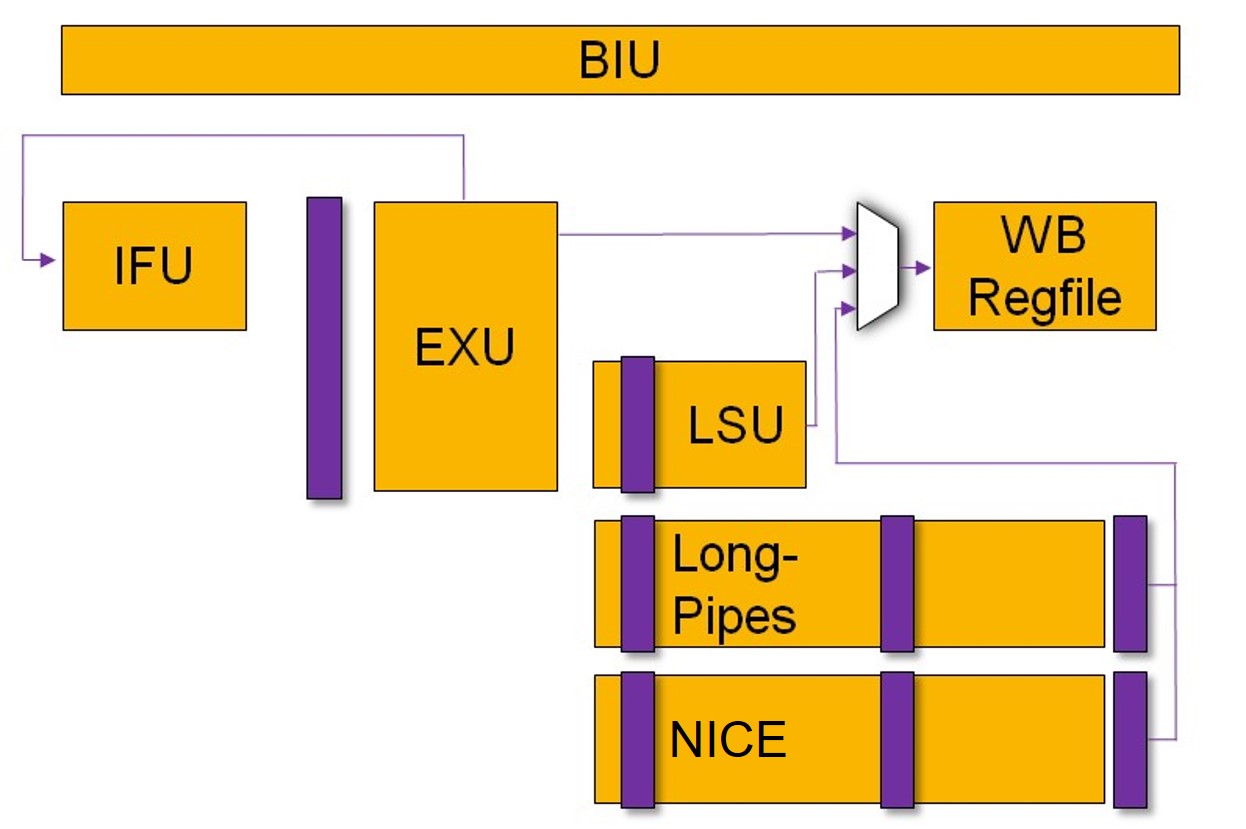

其流水线结构如下:

- First stage: Fetch(IFU)

- Second stage: Decode(EXU), Execute(EXU), Write Back(WB)

- Other stage: Memory Access(LSU

实际上E203 core的流水级是可变的,第一个stage是 Fectch第二个stage是Decode/Execute/write back. 所以我们称他为2级流水RISC-V处理器。

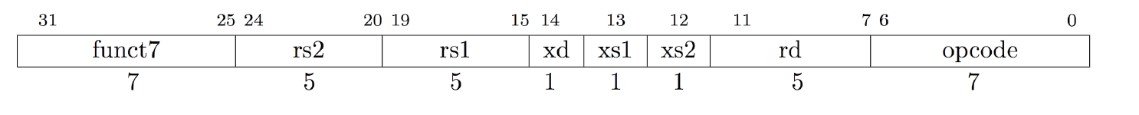

NICE介绍:

支持用户通过自定义指令扩展处理器功能,即NICE(Nuclei Instruction Co-unit Extension)是蜂鸟E203处理器核心的可配置扩展接口。

即当inst[1:0]=11时候 支持32-bit instruction opcode of RISC-V ,用户通过4组定义指令组(Custom-0/1/2/3)扩展。

每个字段含义 可以参考其官方介绍 这里不展开了。

NICE接口包括以下几个channel:

1.Request Channel.

2.Response Channel.

3.Memory Request Channel.

4.Memory Response Channel.

其他比如软件包:

https://github.com/riscv-mcu/hbird-sdk